# TESTING AND EXPOSING WEAK GRAPHICS PROCESSING UNIT MEMORY MODELS

by

Tyler Rey Sorensen

A thesis submitted to the faculty of

The University of Utah

in partial fulfillment of the requirements for the degree of

Master of Science

in Computer Science

School of Computing

The University of Utah

December 2014

Copyright © Tyler Rey Sorensen 2014

All Rights Reserved

# THE UNIVERSITY OF UTAH GRADUATE SCHOOL

# STATEMENT OF THESIS APPROVAL

The thesis of Tyler Rey Sorensen has been approved by the following supervisory committee members:

# THIS PAGE IS A PLACE HOLDER ONLY

Please use the updated form on the Thesis Office website

| Ganesh Gopalakrishnan , Chair enter date |               |

|------------------------------------------|---------------|

|                                          | Date Approved |

| Zvonimir Rakamaric , Member              |               |

|                                          | Date Approved |

| Mary Hall , Member                       |               |

|                                          | Date Approved |

# **ABSTRACT**

Graphics Processing Units (GPUs) are highly parallel shared memory microprocessors, and as such, they are prone to the same concurrency considerations as their traditional multicore CPU counterparts. In this thesis, we consider shared memory consistency, i.e. what values can be read when issued concurrently with writes on current GPU hardware. While memory consistency has been relatively well studied for CPUs, GPUs present substantially different concurrency systems with an explicit thread and memory hierarchy. Because documentation on GPU memory models is limited, it remains unclear what behaviors are allowed by current GPU implementations.

To this end, this work focuses on testing shared memory consistency behavior on NVIDIA GPUs. We present a format for describing GPU memory consistency tests (dubbed GPU litmus tests) which includes the placement of testing threads into the GPU thread hierarchy (e.g. cooperative thread arrays, warps) and memory locations into GPU memory regions (e.g. shared, global). We then present a framework for running GPU litmus tests under system stress designed to trigger weak memory model behaviors, that is, executions that do not correspond to an interleaving of the instructions of the concurrent program. We discuss GPU specific incantations (i.e. heuristics) which we found to be crucial for observing weak memory model executions; these include bank conflicts and custom GPU memory stressing functions.

We then report the results of running GPU litmus tests in this framework and show that we observe a controversial relaxed coherence behavior on older NVIDIA chips. We present several examples of published GPU applications which may exhibit unintended behavior due to the lack of fence synchronization; one such example is a spin-lock published in the popular CUDA by Example book. We then test several families of tests and compare our results to a proposed operational GPU memory model and show that the model is unsound (i.e. disallows behaviors that we observe on hardware). Our techniques are implemented in a modified version of a memory model testing tool named litmus.

# CONTENTS

| AE  | STRACT                                 | iii  |

|-----|----------------------------------------|------|

| LIS | ST OF FIGURES                          | vi   |

| LIS | ST OF TABLES                           | viii |

| AC  | CKNOWLEDGMENTS                         | ix   |

| CH  | IAPTERS                                |      |

| 1.  | INTRODUCTION                           | 1    |

|     | 1.1 Thesis Statement and Contributions | 4    |

|     | 1.1.1 Thesis Statement                 | 4    |

|     | 1.1.2 Contributions                    | 4    |

|     | 1.2 Prior Work                         | 5    |

|     | 1.2.1 GPU Memory Models                | 6    |

|     | 1.3 Roadmap                            | 8    |

| 2.  | BACKGROUND                             | 10   |

|     | 2.1 GPU Programming Model              | 10   |

|     | 2.2 GPU Architecture                   | 13   |

|     | 2.2.1 Hardware Memory Banks            | 14   |

|     | 2.3 PTX                                | 15   |

|     | 2.3.1 CUDA to PTX Mappings             | 16   |

|     | 2.4 Memory Models and Litmus Tests     | 18   |

|     | 2.5 GPU Litmus Tests                   | 20   |

|     | 2.5.1 GPU Configurations               | 22   |

| 3.  | GPU TESTING FRAMEWORK                  | 24   |

|     | 3.1 PTX GPU .litmus Format             | 25   |

|     | 3.2 GPU Program Skeleton               | 27   |

|     | 3.3 Critical Incantations              | 29   |

|     | 3.3.1 General Bank Conflicts           | 30   |

|     | 3.3.2 Memory Stress                    | 32   |

|     | 3.4 Extra Incantations                 | 33   |

|     | 3.4.1 Random Threads                   | 33   |

|     | 3.4.2 Synchronization                  | 34   |

|     | 3.5 Effectiveness of Incantations      | 35   |

|     | 3.5.1 Inter-CTA Incantations           | 35   |

|     | 3.5.2 Intra-CTA Incantations           | 36   |

| 4. NOTABLE RESULTS AND CASE STUDIES                 | 39 |

|-----------------------------------------------------|----|

| 4.1 Notations and Considerations                    |    |

| 4.2 Coherence of Read-Read (CoRR)                   |    |

| 4.3 Fermi Memory Annotations                        |    |

| 4.3.1 Message Passing Through L1                    |    |

| 4.3.2 Mixing Memory Annotations                     |    |

| 4.3.3 CUDA Programming Consequences                 |    |

| 4.4 Volatile Operators                              |    |

| 4.5 Spin-Locks                                      |    |

| 4.5.1 CUDA by Example                               |    |

| 4.5.2 Efficient Synchronization Primitives for GPUs |    |

| 4.6 Dynamic Work Balancing                          |    |

| 4.6.1 CTA Level Work Stealing Deques                |    |

| 4.6.2 Synchronization Between Owner and Thief       |    |

| 4.6.3 Test Distillation                             |    |

| 4.0.4 Test Results                                  | 54 |

| 5. BULK RESULTS                                     |    |

| 5.1 Naming and Synchronization                      | 56 |

| 5.1.1 Different Kinds of Synchronization            | 57 |

| 5.2 Test Specifications and Results                 |    |

| 5.2.1 Message Passing (MP)                          |    |

| 5.2.2 Load Delaying (LD)                            |    |

| 5.2.3 Store Buffering (SB)                          |    |

| 5.2.4 IRIW                                          |    |

| 5.2.5 Coherence of Independent Writes (2+2W)        |    |

| 5.2.6 Fences and Coherence Version 1 (R)            | 64 |

| 5.2.7 Fences and Coherence Version 2 (S)            |    |

| 5.3 High-Level Observations                         |    |

| 5.4 Comparison to Operational Model                 |    |

| 5.4.1 Comparison Results                            | 68 |

| 6. CONCLUSION AND FUTURE WORK                       | 71 |

| 6.1 Additional GPU Configurations                   | 71 |

| 6.2 Herd Model                                      |    |

| 6.3 OpenCL Compilation                              |    |

| 6.4 Summary                                         |    |

| APPENDIX: PTX FROM DYNAMIC LOAD BALANCING           | 76 |

| DEFEDENCES                                          | 79 |

# LIST OF FIGURES

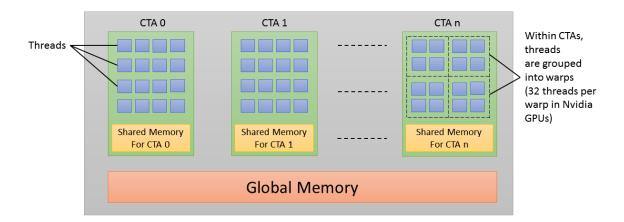

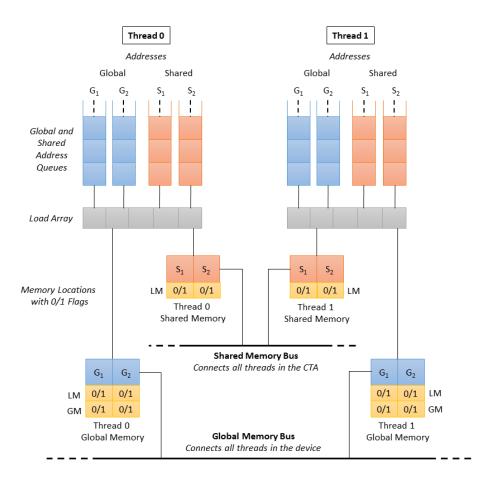

| 2.1 | GPU thread and memory hierarchy of the GPU programming model                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 12 |

|-----|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

| 2.2 | Vector addition GPU kernel written in CUDA                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 12 |

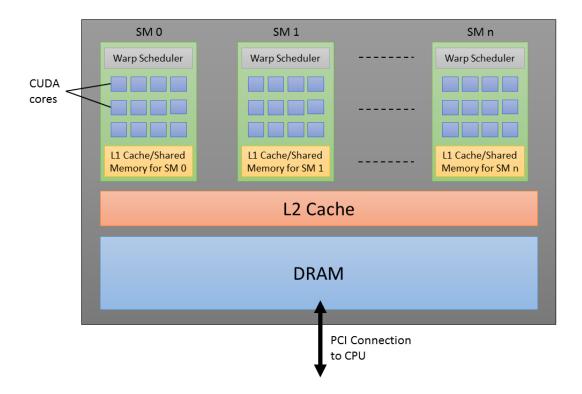

| 2.3 | GPU hardware showing CUDA cores, SMs, and the memory hierarchy                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 14 |

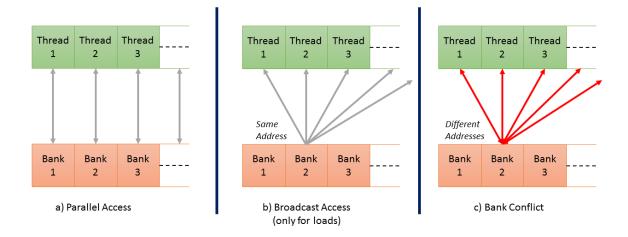

| 2.4 | Different types of concurrent memory accesses within a warp: a) parallel access where threads reads different banks, b) broadcast access where threads read from the same bank and same address, and c) bank conflict access where threads access the same bank but different addresses                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 15 |

| 2.5 | Store buffering (SB) litmus test                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 19 |

| 2.6 | All interleaving of the store buffering (SB) litmus test                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 20 |

| 2.7 | Histogram of results from running the store buffering litmus test on an Intel i7 x86 processor                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 20 |

| 2.8 | Litmus test example written for GPUs in PTX syntax                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 21 |

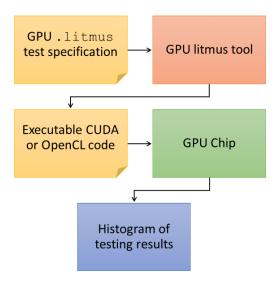

| 3.1 | High-level flow of the GPU litmus tool                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 24 |

| 3.2 | Example of a GPU .1itmus file which specifies the store buffering (SB) test $% \left( 1\right) =\left( 1\right) \left( 1\right) +\left( 1\right) \left( 1\right) \left( 1\right) +\left( 1\right) \left( 1\right) \left( 1\right) \left( 1\right) +\left( 1\right) \left( 1\right) \left( 1\right) \left( 1\right) +\left( 1\right) \left( 1\right) \left( 1\right) \left( 1\right) \left( 1\right) +\left( 1\right) \left( 1\right) \left( 1\right) \left( 1\right) \left( 1\right) +\left( 1\right) \left( 1\right)$ | 25 |

| 3.3 | Additional examples of scope tree declarations                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 26 |

| 3.4 | Testing loop of the CPU portion of the generated program                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 28 |

| 3.5 | The kernel code where GPU threads execute the tests specified in the GPU .litmus file                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 29 |

| 3.6 | Code snippet of the general bank conflict in<br>cantation implementation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 31 |

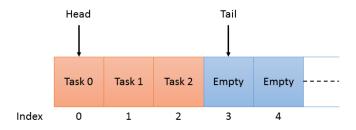

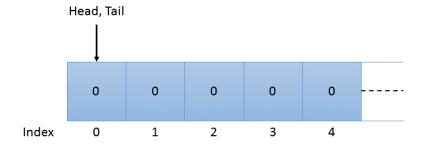

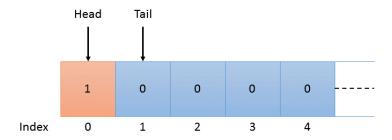

| 3.7 | High-level structure of the memory stress in<br>cantation implementation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 33 |