# United States Patent [19]

## Fant et al.

[11] Patent Number:

atent Number: 5,664,212

[45] Date of Patent:

Sep. 2, 1997

### [54] NULL CONVENTION LOGIC SYSTEM

[75] Inventors: Karl M. Fant; Scott A. Brandt, both

of Minneapolis, Minn.

[73] Assignee: Theseus Research, Inc., St. Paul,

Minn.

[21] Appl. No.: 220,636

[22] Filed: Mar. 31, 1994

# Related U.S. Application Data

[63] Continuation of Ser. No. 74,288, Jun. 8, 1993, Pat. No. 5,305,463, which is a continuation of Ser. No. 702,016, May 11, 1991, abandoned.

| [51]   | Int. Cl.6 |                                         |         | G06F    | 1/00 |

|--------|-----------|-----------------------------------------|---------|---------|------|

| [52] - | U.S. Cl.  | *************************************** | 395/141 | ; 364/9 | 36.1 |

## [56] References Cited

#### U.S. PATENT DOCUMENTS

#### FOREIGN PATENT DOCUMENTS

0 566 739 A1 10/1993 European Pat. Off. . 0 570 584 A1 11/1993 European Pat. Off. . 0 578 821 A1 1/1994 European Pat. Off. . WO92/12498 7/1992 WIPO. WO92/16971 WIPO. 10/1992 WO94/03929 2/1994 WIPO.

# OTHER PUBLICATIONS

Tadashi Shibata & Tadahiro Ohmi, A Functional MOS Transistor Featuring Gate-Level Weighted Sum and Threshold Operations, IEEE Transactions On Electron Devices, Dec. 1992, vol. 39, No. 6, pp. 1444–1455.

Mark Edward Dean, Strip: A Self-Timed Risc Processor, Jun. 1992.

Daniel Hampel & Robert Winder, Threshold Logic, IEEE Spectrum, Apr. 1971, pp. 32–39.

Janusz A. Brzozowski & Carl-Johan H. Seger, Asynchronous Circuits—Monographs in Computer Science, Springer-Verlag New York, Inc., 1995, New York, NY.

M.R. Greenstreet, T.E. Williams, and J. Staunstrup, Self-Timed Iteration, Elsevier Science Publishers B.V. (North-Holland), IFIP, 1988, pp. 309-322.

Teresa H.-Y. Meng, Robert W. Brodersen, and David G. Messerschmitt, Automatic Synthesis of Asynchronous Circuits from High-Level Specifications, IEEE Transactions on Computer-Aided Design, vol. 8, No. 11, Nov. 1989, pp. 1185-1205.

Ted Williams, Latency and Throughput Tradeoffs in Self-Timed Speed-Independent Pipelines and Rings, Stanford University Technical Report No. CSL-TR-91-482, May 1991.

Jens Sparso and Jorgen Staunstrup, Delay-insensitive multi-ring structures, Integration, the VLSI Journal 15, 1993, Elsevier Science Publishers B.V., pp. 313-340.

(List continued on next page.)

Primary Examiner—David Y. Eng Attorney, Agent, or Firm—Steptoe & Johnson LLP

#### [57] ABSTRACT

A Null convention logic system for processing NULL convention signals is comprised of interconnected processing elements. NULL convention signals can assume at least a first meaningful value indicating data and a NULL value which has no data significance. Processing elements receive a plurality of NULL convention signals and produce a meaningful output data value when the number of meaningful input data values exceeds a threshold number. The gates assert a NULL output when all inputs are in the NULL state. Processing elements exhibit hysteresis such that, as the number of meaningful input values falls below the threshold number, the element holds a meaningful output value (or a non-data non-NULL value) until all inputs are in the NULL state. The threshold number may be less than the total number of inputs. Groups of elements may be interconnected, and thresholds selected, to perform logic and other processing functions asynchronously on meaningful signal values.

# 36 Claims, 35 Drawing Sheets

#### OTHER PUBLICATIONS

Tzyh-Yung Wuu and Sarma B.K. Vrudhula, A Design of a Fast and Area Efficient Multi-Input Muller C-element, IEEE Transactions on VLSI Systems, vol. 1, No. 2, Jun. 1993, pp. 215–219.

Marc Renaudin and Bachar El Hassan, The Design of Fast Asynchronous Adder Structures and Their Implementation Using D.C.V.S. Logic, Int'l. Symposium on Circuits & Systems, vol. 4, 1994, pp. 291–294.

Richard G. Burford, Xingcha Fan and Neil W. Bergmann, An 180 Mhz 16 bit Multiplier Using Asynchronous Logic Design Techniques, IEEE 1994 Custom Integrated Circuits Conference, pp. 215–218.

Ted Williams, Self-Timed Rings and Their Application to Division, Stanford University Technical Report No. CSL-TR-91-482, May 1991.

David E. Muller, Asynchronous Logics and Application to Information Processing, Stanford University Press, Switching Theory In Space Technology, pp. 289–297, 1963.

Narinder Pal Singh, A Design Methodology For Self-Timed Systems, Massachusetts Institute of Technology, MIT/LCS/TR-258, Feb. 1981.

T.S. Anatharaman, A Delay Insensitive Regular Expression Recognizer, Dept. of Computer Science, Carnegie-Mellon University, CMU-CS-89-109, Jan. 1989.

Jens Sparso, et al., Design of Delay Insensitive Circuits Using Multi-Ring Structures, European Design Automation Conference, IEEE 0-8186-2780, pp. 15-20, Aug. 1992.

Lawrence G. Heller, et al., Cascode Voltage Switch Logic: A Different CMOS Logic Family, ISSCC 84 Digest of Technical Papers, IEEE, pp. 16–17, Feb. 1984.

Lars S. Nielsen and Jens Sparso, A Low-Power Asynchronous Data-Path For A FIR Filter Bank, IEEE 0-8186-7298-Jun. 1996, pp. 197-207, Jun. 1996.

Stephen H. Unger, Asynchronous Sequential Switching Circuits, 1969, pp. 221, 229.

Carver Mead, Lynn Conway, Introduction to VLSI Systems, 1980, pp. 242–262.

Ivan E. Sutherland, Micropipelines, Jun. 1989, vol. 32, No. 6, Communications of the ACM.

Wojcik et al., On the Design of Three Valued Asynchronous Module, IEEE Transactions on Computers, vol. C-29, No. 10, Oct. 1980, pp. 889-898.

FIG. 1

FIG. 2

FIG. 3

FIG. 4

Sep. 2, 1997

FIG. 6

FIG. 7

FIG. 8

FIG. 9

FIG. 10

FIG. 11

FIG. 12

FIG. 16

FIG. 18

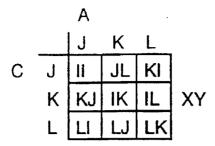

FIG. 19

FIG. 21c

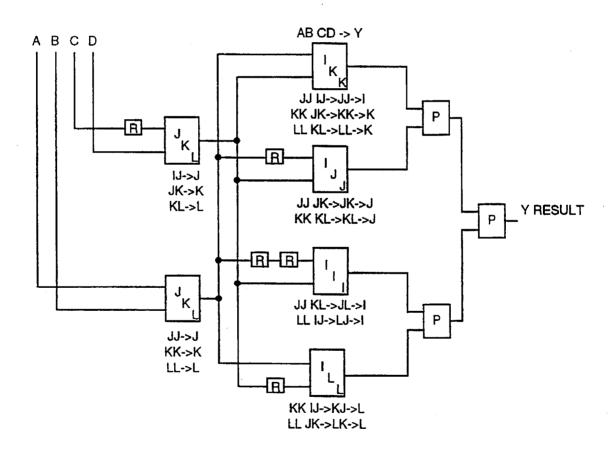

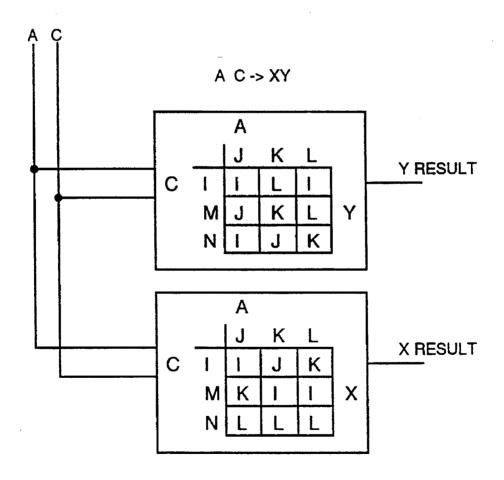

FIG. 22a

FIG. 22b

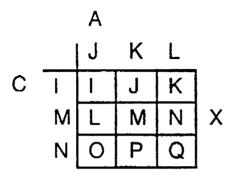

FIG. 23a

FIG. 23b

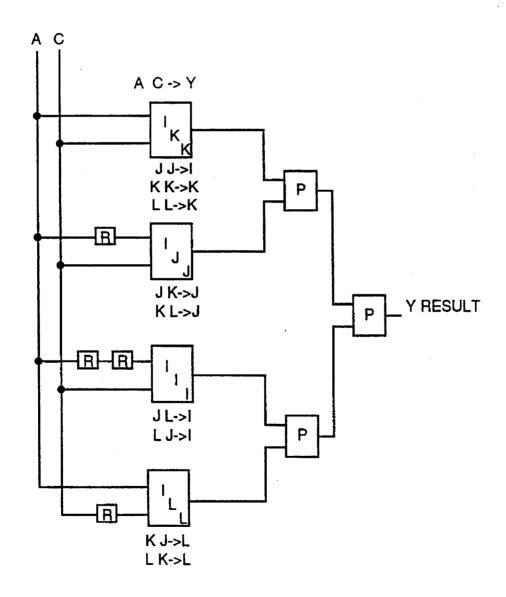

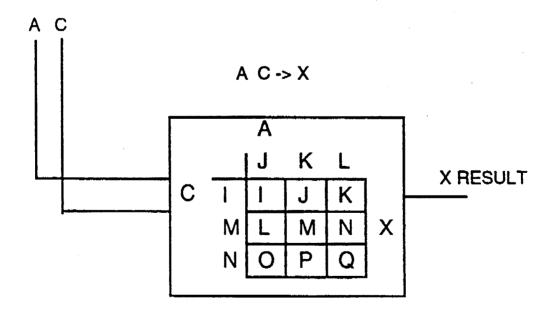

FIG. 24a

FIG. 24b

|   | J | K | L |

|---|---|---|---|

| T | C | V | W |

| М | R | S | Т |

| N | 0 | Р | Q |

|   | Α | В | С |

|---|---|---|---|

| Χ | 0 | 1 | 2 |

| Υ | 3 | 4 | 5 |

| Z | 6 | 7 | 9 |

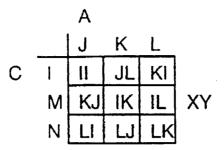

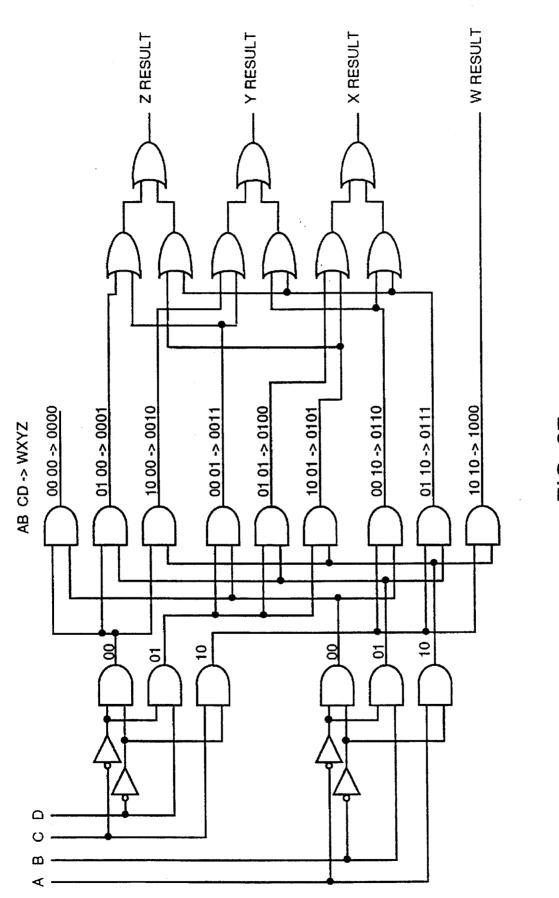

FIG. 25a

FIG. 25b

|    |    | AB   |      |      |

|----|----|------|------|------|

| _  |    | 11   | IJ   | JI   |

| CD | =  | 1111 | IIIJ | IIJI |

| •  | IJ | IIJJ | IJII | IJIJ |

|    | JI | IJIJ | IJIJ | JIII |

**WXYZ**

|    |    | AB   |      |      |

|----|----|------|------|------|

|    |    | 00   | 01   | 10   |

| CD | 00 | 0000 | 0001 | 0010 |

|    | 01 | 0011 | 0100 | 0101 |

|    | 10 | 0110 | 0111 | 1000 |

**WXYZ**

FIG. 26a

FIG. 26b

FIG. 27

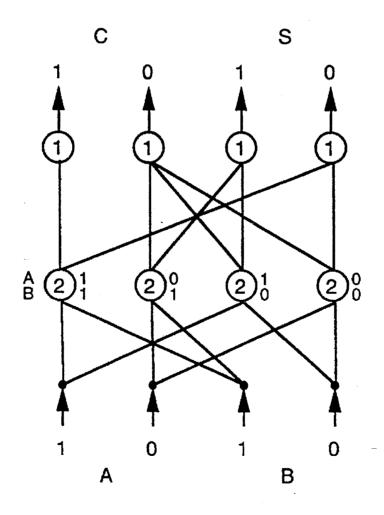

| A | В | S | С |

|---|---|---|---|

| 0 | 0 | 0 | 0 |

| 0 | 1 | 1 | 0 |

| 1 | 0 | 7 | 0 |

| 1 | 1 | 0 | 1 |

FIG. 28a

FIG. 28b

FIG. 29

FIG. 30

FIG. 31a

FIG. 31b

FIG. 32a

|        | S | N |   |   |   | Α |   |   |   |   |   |   |   | В |   |   |   |   |

|--------|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|

| INPUT  | Α | - | N |   | X |   |   | Y |   |   | N |   |   | X |   |   | Υ |   |

|        | В | 1 |   |   |   |   | Z |   |   |   |   |   |   |   |   |   |   |   |

| RESULT | Ō | Z | Z | X | X | X | Y | Y | Y | Z | X | > | N | X | Y | Z | X | Y |

FIG. 32b

FIG. 33

Sep. 2, 1997

FIG. 34

FIG. 36

FIG. 37

FIG. 38

FIG. 39a

| O               |   |   |   |   | N |   |   |   |   |   |   |   | - | Υ |   |   |   |   |

|-----------------|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|

| INPUT I1        |   | N |   |   | X |   |   | Y |   |   | N |   |   | Χ |   |   | Υ |   |

| · 12            | N | X | Y | Ν | X | Y | N | X | Υ | N | X | Υ | N | X | Υ | N | X | Y |

| <b>RESULT O</b> | N | N | Z | Ν | Y | Y | N | Y | Υ | N | Y | Y | Y | Y | Y | Y | Y | Y |

FIG. 39b

FIG. 40

FIG. 41

|               | EN  |                    |                           |                   | N                        | ţ.     |                           |                   | }                        |              |              |                 |                 |                    | , , <del>, ,</del> |                          |                          |

|---------------|-----|--------------------|---------------------------|-------------------|--------------------------|--------|---------------------------|-------------------|--------------------------|--------------|--------------|-----------------|-----------------|--------------------|--------------------|--------------------------|--------------------------|

|               | PNV |                    | 1                         | 1                 | 1                        |        |                           | /                 |                          |              | - 1          | 1               |                 |                    |                    | <del></del> /            |                          |

| INPUT<br>NAME | ANV | 1                  | <u> </u>                  |                   | /                        | ľ      | 1                         | V                 | /                        | ١            |              |                 | /               | 1                  | 1                  | \                        | /                        |

| INAIVIE       | NA  | Ν                  | ٧                         | N                 | ٧                        | Z      | ٧                         | N                 | ٧                        | Ν            | ٧            | N               | ٧               | N                  | ٧                  | Ν                        | ٧                        |

|               | OA  | Ν                  | N                         | Ν                 | N                        | N      | N                         | Ν                 | N                        | Ν            | N            | N               | N               | Ν                  | Ν                  | ٧                        | ٧                        |

| RESULT        | DN  | N                  | N                         | Z                 | ٧                        | Z      | N                         | Ν                 | ٧                        | Z            | Z            | Ν               | N               | N                  | Ν                  | Ν                        | Z                        |

|               | EN  | N                  | N                         | N                 | N                        | ٧      | N                         | Ν                 | N                        | 7            | Z            | Ν               | N               | ٧                  | Ν                  | ٧                        | ٧                        |

| STATES        |     | 1                  | 2                         | 3                 | 4                        | 5      | 6                         | 7                 | 8                        | 9            | 10           | 11              | 12              | 13                 | 14                 | 15                       | 16                       |

|               |     | AWAITING PNV VALID | RESET DN AWA-T-NG NA NULL | AWA-TING NA VALID | SET DN AWAITING ANV NULL | SET EN | RESET DN AWAITING NA NULL | AWAITING NA VALID | SET DN AWA-TING ANV NULL | -NACCESS-BLE | -NACCESS-BLE | RESET EN AND OA | RESET EN AND OA | AWA-T-NG ANV VAL-D | - NACCESS-BLE      | SET OA AWA-T-NG PNV NULL | SET OA AWAITING PNV NULL |

FIG. 42

FIG. 43

DELIVER RESULT NAME SEGUENCE

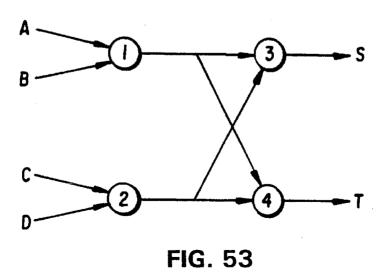

FIG. 47

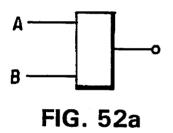

FIG. 48

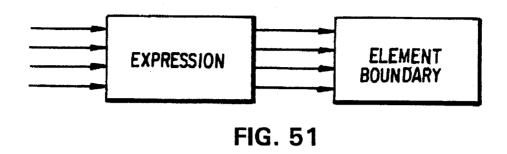

FIG. 49

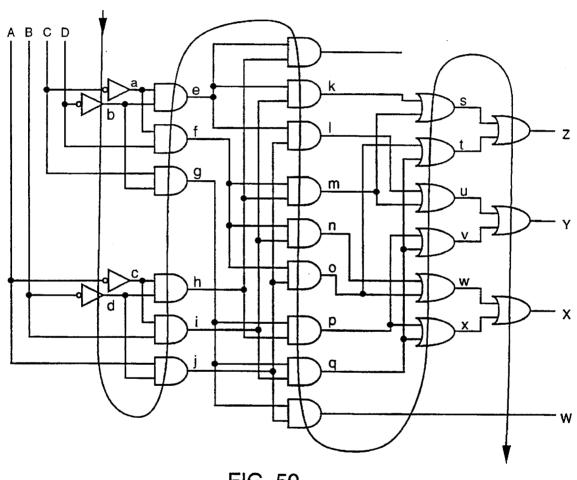

FIG. 50

| IN    | A | N |   | X |   |   | Y |   |

|-------|---|---|---|---|---|---|---|---|

| - 114 | B | 1 | N | X | Y | N | X | Y |

| OUT   | 0 | N | N | X | X | N | X | Y |

FIG. 52b

|        | 0 |   |   |   |   | N  |   |   |   |   | Ι | _ |   |   |   | Y | -  |   |   |   | Γ |   |   |   | X |   |   |   |   |

|--------|---|---|---|---|---|----|---|---|---|---|---|---|---|---|---|---|----|---|---|---|---|---|---|---|---|---|---|---|---|

| INPUT  | Α |   | N |   |   | _X |   |   | Y |   | Τ |   | N |   |   | X |    | Τ | Y |   | П | N |   |   | X |   | Г | Υ |   |

|        | В | N | X | Υ | 7 | X  | Υ | Ν | X | Y |   | N | X | Y | N | X | Y  | N | X | Y | N | X | Y | N | X | Υ | N | X | Y |

| RESULT | 0 | Z | N | N | Z | X  | Υ | Z | Y | Y | 1 | N | Υ | Y | Y | Y | ΊΥ | Υ | Y | Y | N | X | X | X | X | X | X | X | X |

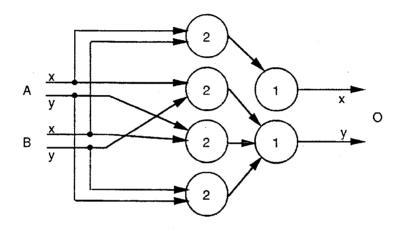

FIG. 54b

FIG. 55

FIG. 56

|         | 0 |   |   |          |   |   |   |   | _ | 7 |   |   |   |   |    |          |    |   |   |   |   |   |   |   | 1 | V |   |    |   |   |   |   |   |

|---------|---|---|---|----------|---|---|---|---|---|---|---|---|---|---|----|----------|----|---|---|---|---|---|---|---|---|---|---|----|---|---|---|---|---|

| INPUT A |   |   | > | <u> </u> |   |   | Y |   |   |   | l |   |   | Γ | Ī  | <u>7</u> |    |   |   | X |   |   | ` | 7 |   |   | Ī |    |   |   |   | Į |   |

|         | В | X | Υ | 1        | Z | X | Y | İ | Z | X | Υ | Π | N | X | Y  | 1        | N  | X | Y | T | N | X | Y | I | N | X | Y | II | N | X | Y |   | N |

| RESULT  | Ö | Y | Y | Υ        | Υ | Υ | Y | Y | Y | Y | Ÿ | Y | Y | Y | ĪΥ | 1        | 'N | Y | Y | N | N | Y | Y | N | N | N | N | N  | N | N | N | N | N |

FIG. 57

|        | Α | N |   |   |          |   |   |   |   |   |   |   |   |   | 1 |   |   |   | D |   |   |   |   |   |   |   |   |   |

|--------|---|---|---|---|----------|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|

| INPUT  | В |   | N |   | <u> </u> |   |   | D |   | Z |   | Ī |   | D |   |   | N |   |   | l |   |   | D |   |   |   |   |   |

|        | C | Z | 1 | D | 2        | _ | D | 2 | 1 | D | 7 | 1 | D | 2 | _ | D | Z | I | D | Ν | ı | D | N | ١ | D | N | ı | D |

| RESULT | 0 | Z | 1 | 1 | 1        |   |   |   |   | 1 | 1 |   |   |   | 1 | 1 |   | 1 | ı | I | 1 | 1 | 1 | 1 | I | 1 | Π | D |

FIG. 58

|        | Α |   |   |   |   | N |   |   |   |   | l |   |   |   |   |   |   |   |   | D |   |   |   |   |   |   |   |   |

|--------|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|

| INPUT  | В |   | N |   | 1 |   |   | D |   |   | N |   |   | 1 |   |   | D |   |   | N |   |   | 1 |   |   | D |   |   |

|        | С | Ν | _ | D | Z |   | D | N | 1 | D | N |   | D | Z |   | D | Z |   | D | N | 1 | D | 2 | 1 | D | Ν | 1 | D |

| RESULT | Ö | Ν | - | 1 |   | _ |   | - | 1 | D | 1 | I | I | _ | Π | I |   | I | D | 1 | 1 | D |   | I | D | D | D | D |

FIG. 59

FIG. 60

FIG. 61

FIG. 62

# **NULL CONVENTION LOGIC SYSTEM**

This is a continuation of application Ser. No. 08/074,288 filed Jun. 8, 1993, now U.S. Pat. No. 5,305,463 which is a continuation of U.S. Ser. No. 07/702,016, filed May 11, 5 1991, now abandoned.

#### BACKGROUND OF THE INVENTION

This invention relates to information processing systems and methods for manipulating and resolving data, and particularly to computer systems and methods. The invention is particularly useful for building circuits, and for building processors utilizing a plurality of such circuits.

Traditional electronic logic circuits are composed of continuously acting logic elements which are continuously asserting a potentially legitimate result. When new input data is presented to a circuit, the result asserted by the circuit might change several times before settling to the correct result. In general it is not possible to determine, in terms of the circuit output itself, when the correct result is asserted by the circuit.

The determination of completion has generally been accomplished by a representation external to the circuit, most often a system clock. Other types of external representations have also been used, such as a delay line associated with each circuit. Such external systems are provided to indicate when the output of the circuit is VALID. They do so by allowing sufficient time for the logic circuit to settle to a correct result before declaring the result values VALID.

External timing of the logic circuit requires that the control and logic representations be carefully engineered to coordinate their timing characteristics. Because they must be coordinated or synchronized, such systems are typically referred to as synchronous systems. In the case of a system clock, the circuit has to be carefully designed so that it is assured of settling to a correct result within one clock period. Similarly, a delay line must be long enough to accommodate the timing of the circuit and it must also be guaranteed that it's delayed control signal will be stable for a long enough time. Such synchronization considerations place significant complications on system design.

The existing technology of speed independent or Muller circuits does not postulate a NULL value integrated into the primitive transform elements. It relies instead on Boolean logic gates carefully arranged to provide the whole circuit with a specific resolution behavior. This cannot, however, eliminate all possible hazards due to circuit element delays. Transmission elements can introduce delays that could cause incorrect function of the circuit. The existing technology is not logically complete in that physical timing characteristics of the circuit element still have to be considered in any circuit design.

Speed independent circuits put the burden of completion integrity on the configuration of the circuit itself and cannot achieve a purely logical expression of the circuit. The NULL convention puts the burden of completion integrity on the primitive transform elements. This allows a purely logical expression of a circuit quite independent of the physical timing behavior of all circuit elements.

A known concept using a non-data representation as a 60 control means is the spacer code of dual rail encoding associated with speed independent circuits. Dual rail encoding, however, is an interface signaling protocol between circuits and is not a concept associated with the internal organization of the circuits themselves.

Despite the need for a system or environment in the art which enables autonomously acting and coordinated logic 2

circuits to implement independently acting and locally controlled process representations without the need for external control representations, and which overcomes the limitations and problems of the prior art, none insofar as is known has been proposed or developed.

Accordingly, it is an object of the present invention to provide an information processing system and method for manipulating and resolving data. Another object of the invention is to provide a system and method which is useful for constructing information processing units and members such as circuits and gates and for constructing configurable processors utilizing a plurality of such circuits and gates.

Yet another object of this invention is to provide a system and method which enables processors having autonomously acting and coordinated logic circuits to implement independently acting locally controlled process representations without the need for external control representations. A further object of the invention is to provide a system and method as described above which utilizes the representation of control as a value with respect to the logic circuits and gates themselves.

Still another object of the invention is to provide a system and method of utilizing a null convention in logic and processor design and function.

#### SUMMARY OF THE INVENTION

The present invention provides an information processing system for manipulating and resolving data, which has at least one information processing unit for resolving combinations of data and non-data values, for example a logic circuit. The information processing unit or units each have at least one information processing member, for example a logic gate, also for resolving data. The unit further has a plurality of information transmission elements, for example conductors, each element transmitting the data to and from the one or more members or units.

The information transmission elements may be electrical, optical or any other transmission means known in the art. Data manipulated and resolved by the system and the system components described above consist of values which, for example, may represent physical states on or in the elements, members and units. Such physical states represent voltage, optical energy or any other medium which may be utilized to convey information pertaining to velocity, temperature, or angular position for example. Importantly, the system and its components also transmit and resolve non-data values.

Each information processing member and unit has one or more information transmission elements connected to itself for both input or presentation of values, and for output or assertion of result values. And, although elements are capable of transmitting only one values at a time, members and units are capable of resolving combinations of values (information) which are presented either individually over time via a single element, or simultaneously via multiple elements.

Allowed values are those which are resolvable by information processing members and units, and consist of at least one data value and at least one non-data value, at least one non-data value being a null value. The set of data values includes a single value or two values, for example, such as is used in traditional binary logic. In addition to the null value, one or more intermediate values, which are distinct from the null value and the data values, may be included in the set or group of allowed values.

Accordingly, in one embodiment of the information processing system of the present invention there are two

allowed values, the first allowed values being a data value and the second allowed value being a null value. In another embodiment, there are three allowed values, the first allowed value being a data value, the second allowed value being a data value, and the third allowed value being a null value. In 5 still another embodiment, there are three allowed values, the first allowed value being a data value, the second allowed value being an intermediate value, and the third allowed value being a null value. In a final embodiment of the present invention, there are four allowed values, the first allowed 10 value being a data value, the second allowed value being a data value, the fourth allowed value being an intermediate value, and the fourth allowed value being a null value.

Each information processing unit maps from combinations of values presented to it to combinations of values to 15 be asserted by it. To achieve play-through, the information processing members resolve values by asserting a value for each combination of values presented to it, such that (1) for valid combinations of presented values the asserted value is a data value dependent upon the particular combination of <sup>20</sup> (b) means for informing all existing preceding bounding presented values, and (2) for invalid combinations of presented values the asserted value is a null value.

To achieve hysteresis, the information processing members resolve values by asserting a value for each combination of values presented such that (1) for valid combinations of presented values the asserted value is a data value dependent upon the particular combination of presented values which remains asserted until the combination of presented values becomes all-null, and (2) for all-null combinations of presented values the asserted value is a null value which remains asserted until the combination of presented values becomes valid.

With respect to intermediate value resolution, information processing members resolve values by asserting a value for each combination of values presented such that (1) for valid combinations of presented values the asserted value is a data value dependent on the particular combination of presented values, (2) for combinations of values including intermediate values the asserted value is an intermediate value and (3) for all-null combinations of presented values the asserted value is a null value.

The information processing unit cycles through resolution and non-resolution states to allow determination of the unit's (1) completion of a data resolution and (2) readiness to  $_{45}$ perform another data resolution. A resolution state occurs when the unit is presented with a valid combination of values and is asserting a valid combination of values. A non-resolution stat occurs when the unit is presented with an all-null combination of values and is asserting an all-null 50 combination of values.

The information processing unit can perform a specific data resolution function by asserting a predetermined combination of values for each combination of presented values. The unit can further store values by asserting a combination 55 of values equal to a previously presented combination of values. The unit can select values by asserting a combination of values which are a subset of a first combination of presented values relative to a second combination of presented values, and can also distribute data by asserting a 60 combination of values equal to a first combination of presented values as a subset of it's combination of asserted values relative to a second combination of presented values.

The information processing system further comprises bounding means for asynchronously coordinating value pre- 65 sentation to the information processing units. Each bounding means comprises a null-valid detector for determining a

unit's (1) completion of a data resolution and (2) readiness to perform another data resolution; means for storing value combinations, and means for communicating with other bounding means.

The null-valid detector is preferably an information processing unit which asserts a null value when it's combination of presented values is all-null and continues asserting a null value until it's combination of presented values becomes valid, whereupon it asserts a data value and continues asserting a data value until it's combination of asserted values becomes all-null. The means for storing is preferably a unit which asserts a combination of values equal to a previously presented combination of values. The communication means comprises:

- (a) means for informing all existing preceding bounding means that a first null-valid detector has detected a valid combination of presented values, the valid combination of presented values has been stored in the storing means, and that all existing preceding bounding means can now assert an all-null combination of values;

- means that the first null-valid detector has detected an all-null combination of presented values and all existing preceding bounding means can now assert a valid combination of values;

- 25 (c) means for detecting that all existing succeeding bounding means have detected and stored a valid combination of values resulting from the valid combination of values stored in the storing means and asserted by the bounding means, whereupon an all-null combination of values can be asserted by the bounding means; and

- (d) means for detecting that all existing succeeding bounding means have detected an all-null combination of values asserted by the bounding means, whereupon a valid combination of values can be asserted by the bounding

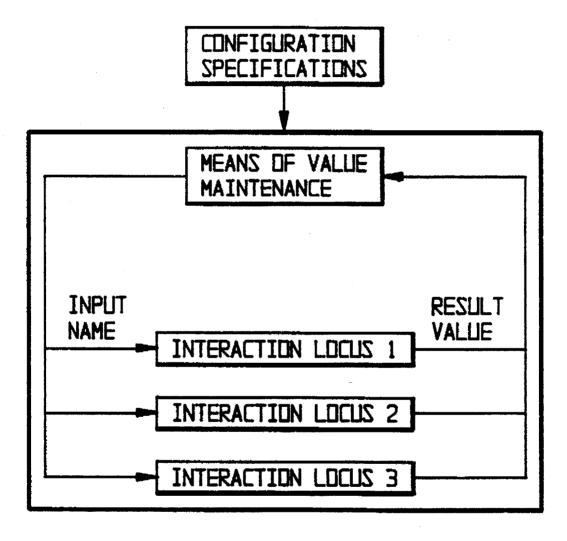

A generally configurable information processing system is constructed of an information processing unit for resolving combinations of values, a unit for storing combinations of values, a unit for configuring value presentation relationships relative to a second combination of values, and bounding means for asynchronously coordinating value presentation between units.

The configuring units, for example a distributor or selector, configure value presentation relationships among at least one resolving unit and at least one storing unit relative to a combination of directive values, for example program instructions, asserted by a first bounding means and presented as the second combination of values of the configuring unit.

A resolution configuration exists during the presentation of a valid combination of directive values to the configuring unit resulting in the presentation of a valid combination of values to the storing unit. A non-resolution configuration exists during the presentation of an all-null combination of directive values to the configuring unit resulting in the presentation of an all-null combination of values to the storing unit.

Data resolution is accomplished by a progression of alternating resolution configurations and non-resolution configurations relative to a progression of combinations of directive values.

These and other benefits of this invention will become clear from the following description by reference to the drawings.

# BRIEF DESCRIPTION OF THE DRAWINGS

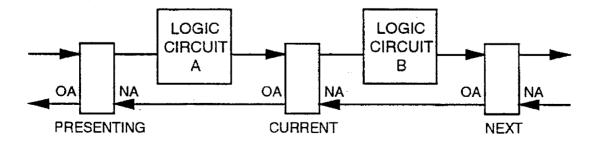

FIG. 1 shows the general structure of null convention logic circuits bounded by boundary elements,

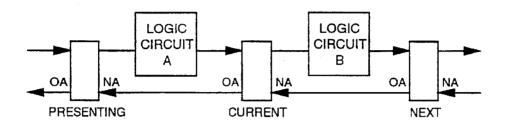

- FIG. 2 shows a network of association relationships with no cycles,

- FIG. 3 illustrates a variable association rule as a bag that isolates variables and also keeps them together,

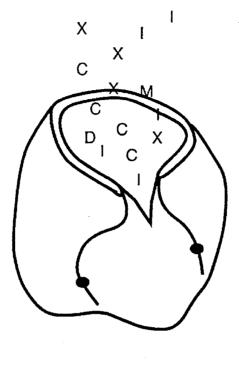

- FIG. 4 illustrates the precedence of occurrence relationships among interactions for the example process,

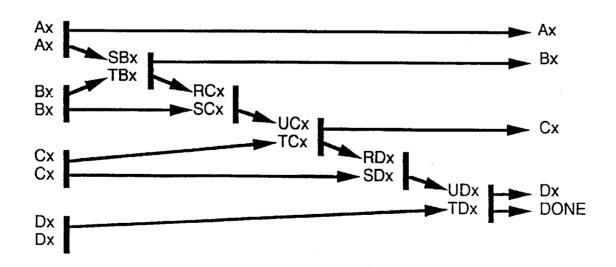

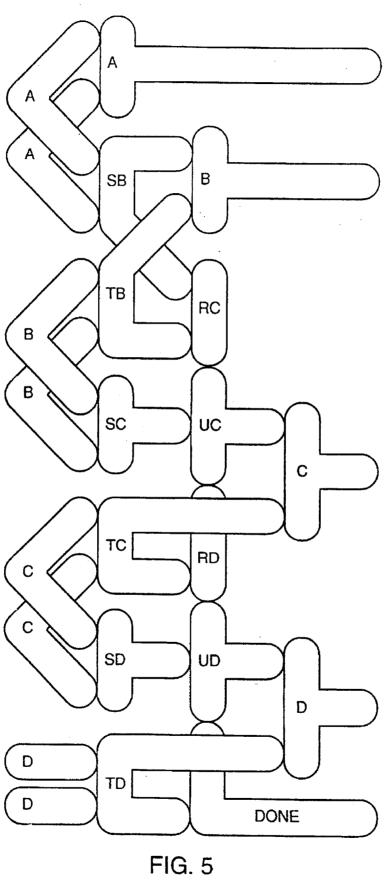

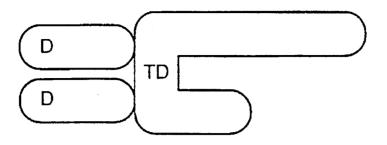

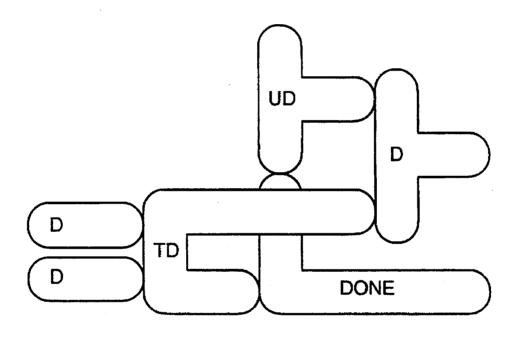

- FIG. 5 shows a rigid structure of interacting variables that might be expected to express the example process,

- FIG. 6 illustrates the relationships between input variables 10 and the result asserting variable,

- FIG. 7 illustrates the difficulty directionality of interaction between directly associated variables,

- FIG. 8 illustrates how many isolation variables must be between any two variables that assert the same value set,

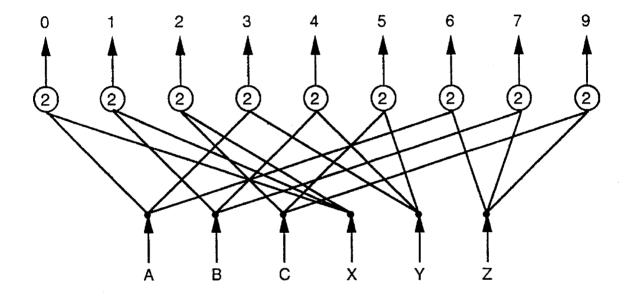

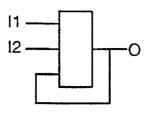

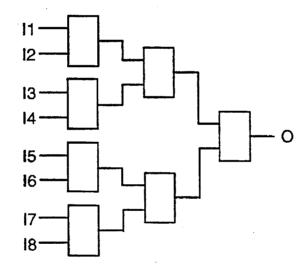

- FIG. 9 illustrates how variables can be arranged in a standard association unit called an interaction locus that isolates identical input and result value sets,

- FIG. 10 shows one way to graphically represent an 20 set to implement a NULL-VALID detector element, interaction locus,

- FIG. 11 shows how several interaction loci can be directly associated to render a larger process expression,

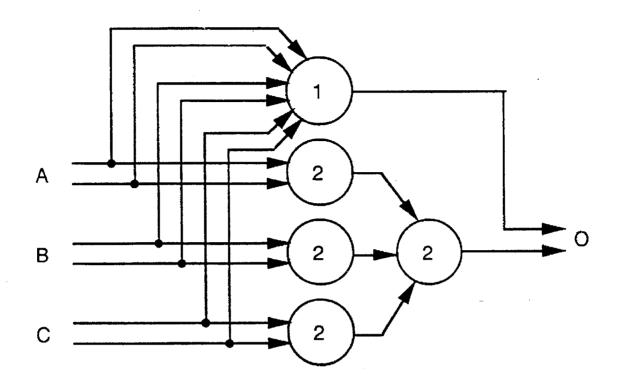

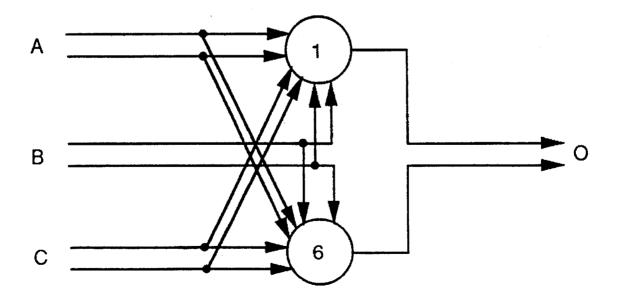

- FIG. 12 shows that the standard graphic form of representing logic circuits is identical to the more general form 25 developed from the theory,

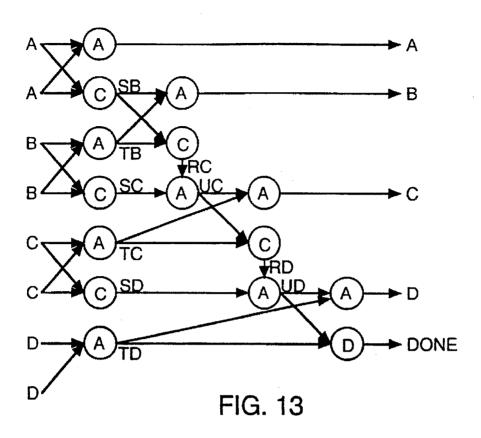

- FIG. 13 is a directly associated expression with interaction loci which still cannot determine its own completion,

- FIG. 14 is a configuration of interaction loci that will work with a NULL value added to the value sets of the interaction loci,

- FIG. 15 illustrates a configuration of rotation loci to convert a given input name to a standard recognition name,

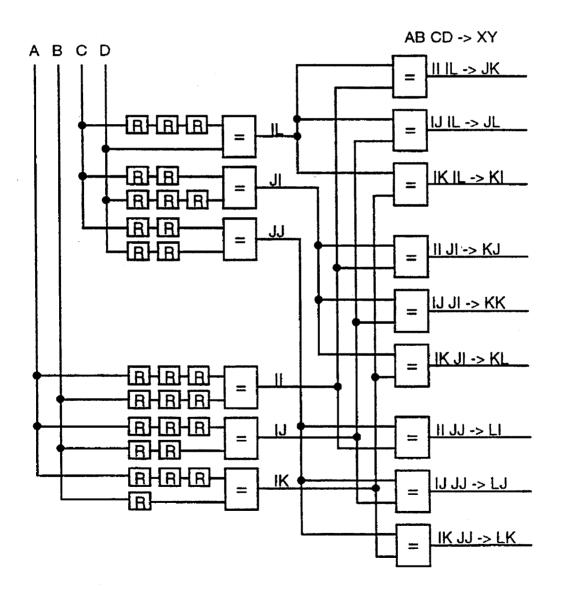

- FIG. 16 is the input section of an expression that will 35 recognize all of the possible input names of the process,

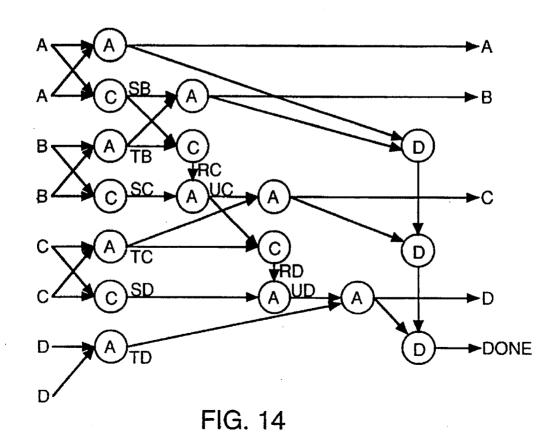

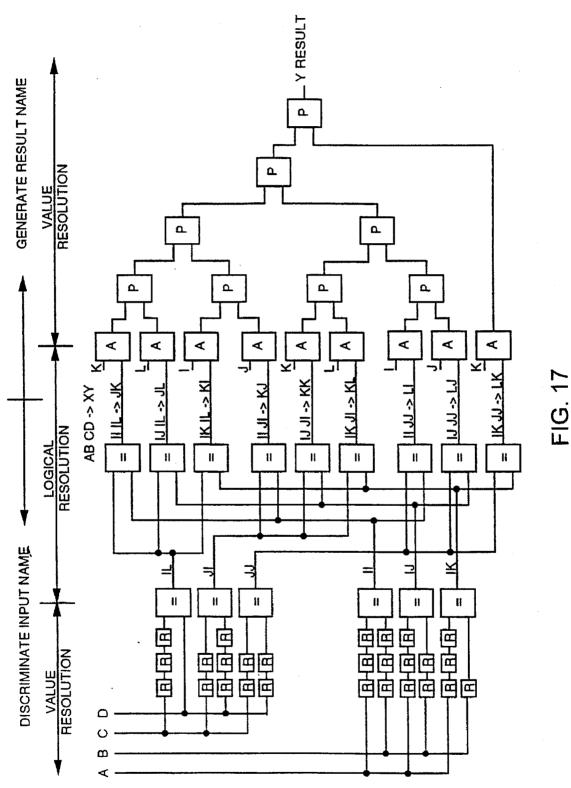

- FIG. 17 is the complete expression that will transform each possible 4 variable-4 value input name to a specific 4 variable-4 value result name,

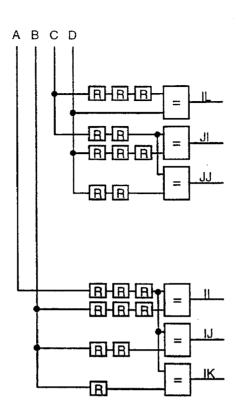

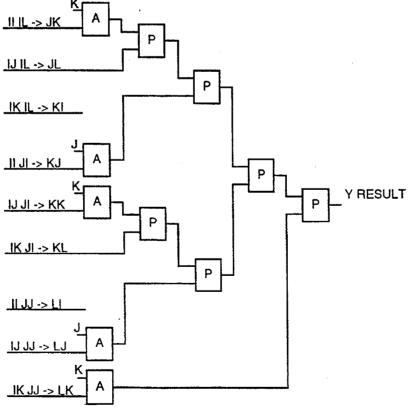

- FIG. 18 shows how the input name recognition stage can 40 be optimized,

- FIG. 19 shows how the result collection and assertion stage can be optimized,

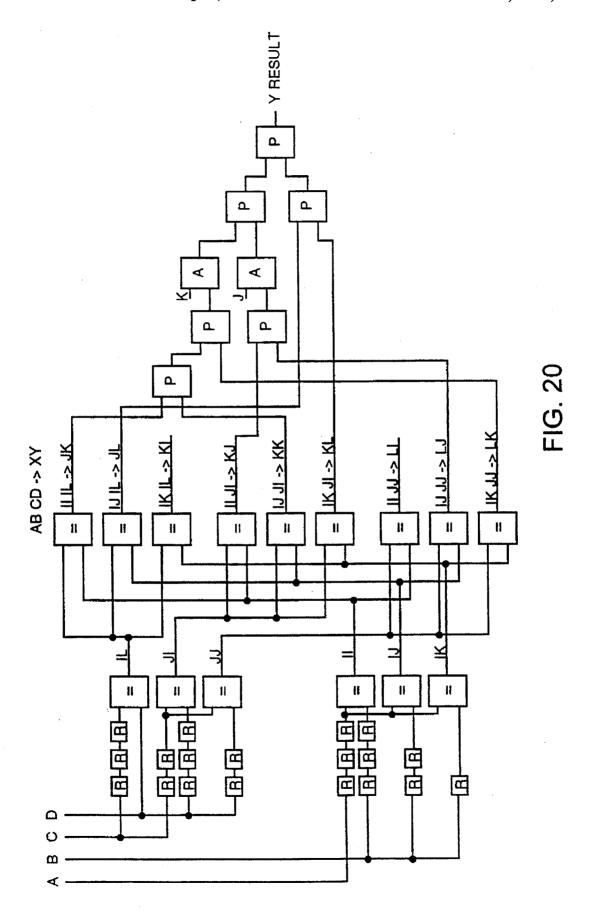

- FIG. 20 shows the complete optimized expression to recognize 4 variable-4 value input names and assert 4 variable-4 value result names,

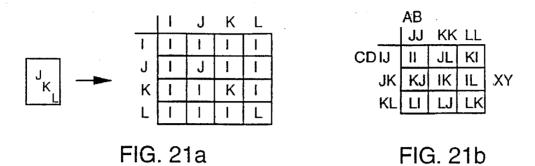

- FIGS. 21a-c illustrate how the expression of the example process can be expressed if custom interaction loci are

- FIGS. 22a-b illustrate how the expression can be further optimized by reassigning the coding of the input names,

- FIGS. 23a-b illustrate the expression of the example process if 6 values are available,

- FIGS. 24a-b illustrate the expression of the example  $^{55}$ process if 9 values are available,

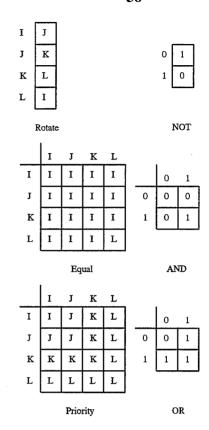

- FIGS. 25a-b show that the expression becomes a pure variable expression if 15 values are available,

- FIGS. 26a-b show the transform table for the example expression if only 2 values are available,

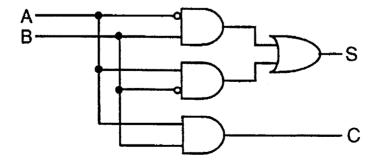

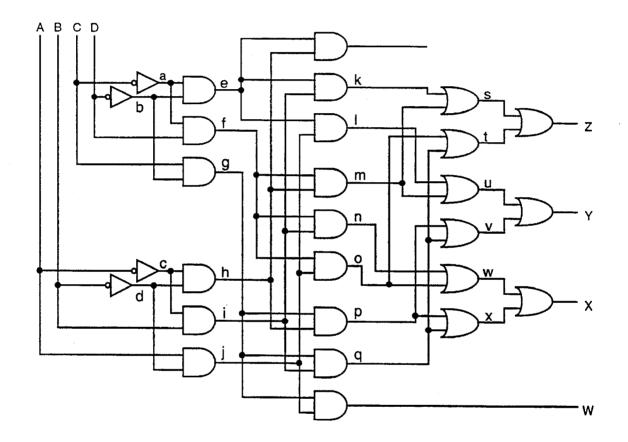

- FIG. 27 shows the example process as a, prior art, standard logic circuit,

- FIGS. 28a-b show the 2 value NULL convention expression of the simpler example process of FIG. 12,

- FIG. 29 shows the basic example process expressed as 2 value NULL convention logic,

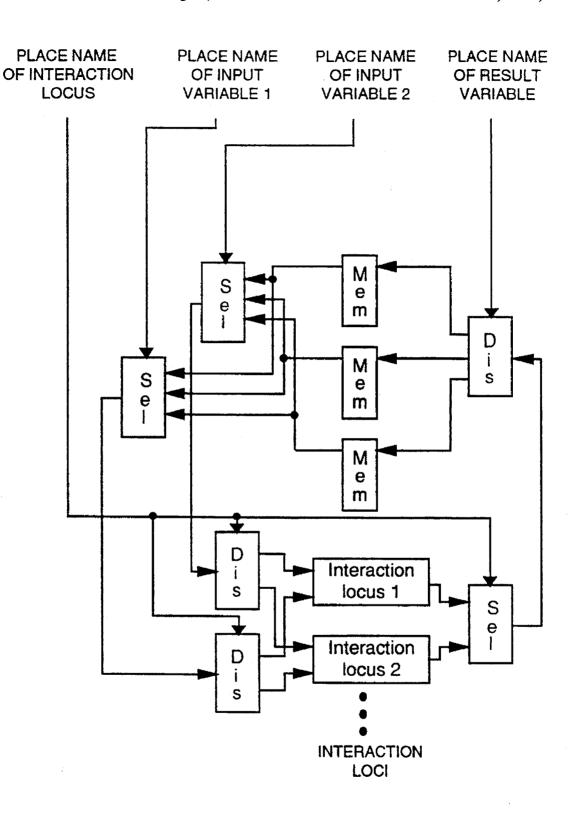

- FIG. 30 illustrates the general form for a generally configurable process,

- FIGS. 31a and 31b show a variable structure and transform rule set to implement a memory element,

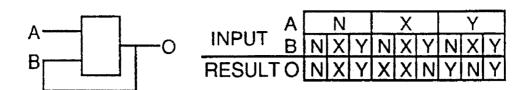

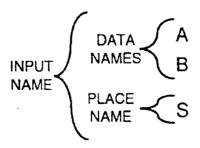

- FIGS. 32a-b show a variable structure and transform rule set to implement a selector element

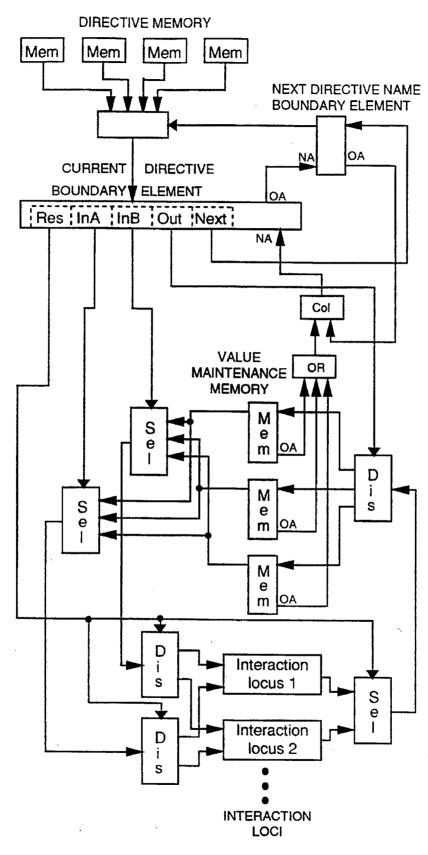

- FIG. 33 illustrates the composite name form for a generally configurable processor,

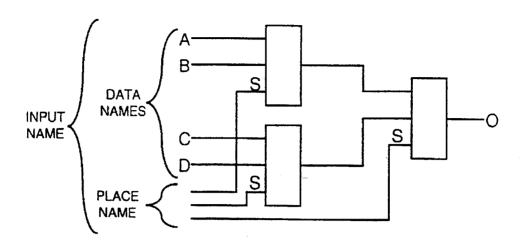

- FIG. 34 illustrates a selector element structure,

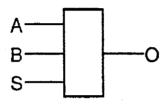

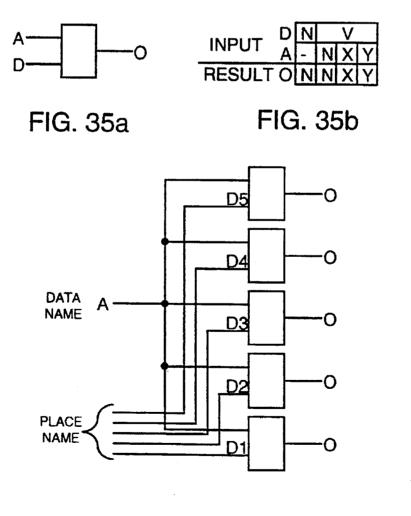

- FIGS. 35a-b show a variable structure and transform rule set to implement a distributor element,

- FIG. 36 illustrates a distributor element structure,

- FIG. 37 illustrates the portion of a generally configurable process expression that configures association relationships for each interaction,

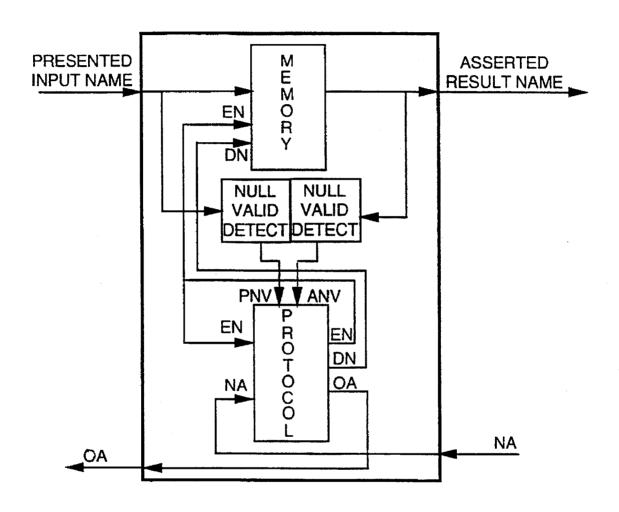

- FIG. 38 shows the structure of the boundary element,

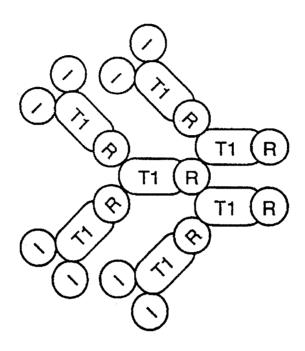

- FIGS. 39a-b show a variable structure and transform rule

- FIG. 40 shows how a NULL-VALID detector can be cascaded to accommodate any size name,

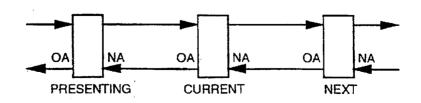

- FIG. 41 shows how boundary elements communicate to synchronize value flow,

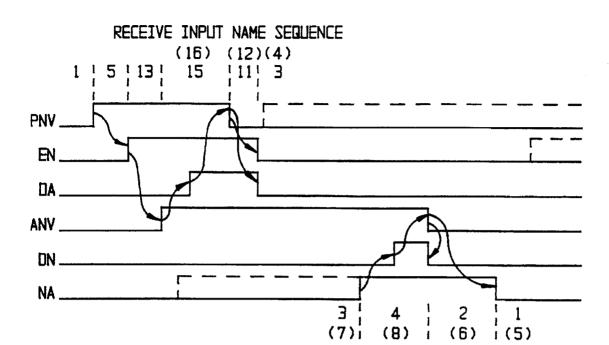

- FIG. 42 is the transform table for the protocol section of the boundary element,

- FIG. 43 shows the value change timing relationships among the variables of the boundary element,

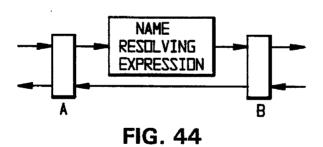

- FIG. 44 illustrates how name resolving expressions are inserted between boundary elements to form larger expressions.

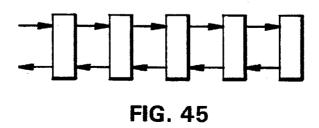

- FIG. 45 illustrates how boundary elements can be pipelined.

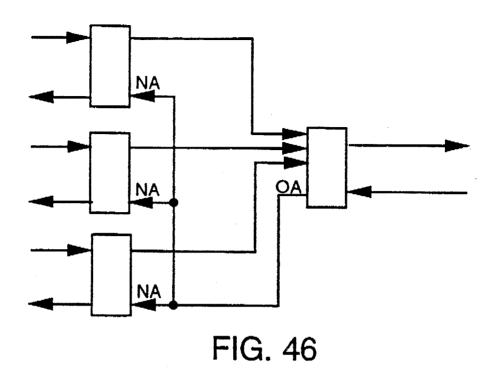

- FIG. 46 shows a fan in configuration of boundary elements.

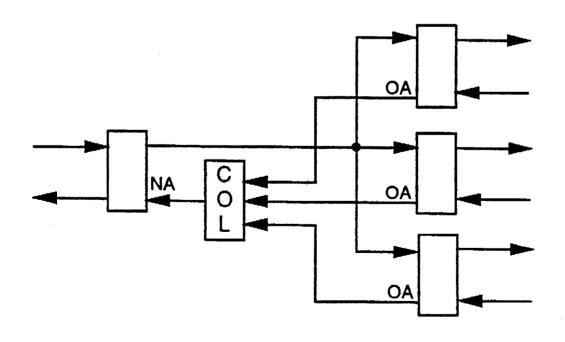

- FIG. 47 shows a fan out configuration of boundary elements.

- FIG. 48 show the complete generally configurable process expression.

- FIG. 49 is an example process expression to be mapped into the generally configurable process,

- FIG. 50 shows the sequence thread of interactions for the 45 generally configurable process to perform one at a time,

- FIG. 51 shows an expression bounded by a boundary element that will determine its resolution completion,

- FIGS. 52a-b show a typical variable structure and transform rule set that does not guarantee the integrity of the 50 NULL value wavefront,

- FIG. 53 shows an expression for which the NULL value wavefront is not completely determinable,

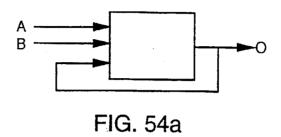

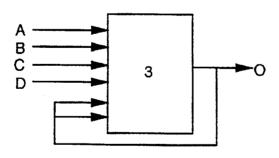

- FIGS. 54a-b show a variable structure and transform rule set that provides a hysteresis solution to the NULL value wavefront problem,

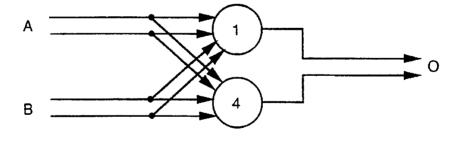

- FIG. 55 shows the feedback configuration to provide a 1 DATA value threshold locus with hysteresis to make the NULL wavefront determinable,

- FIG. 56 illustrates an expression with encoded values and hysteresis interaction loci,

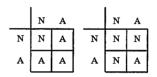

- FIG. 57 shows how a NULL-VALID detector can be specified with INTERMEDIATE values,

- FIG. 58 shows a threshold 3 INTERMEDIATE value 65 interaction locus with 3 input variables,

- FIG. 59 shows a threshold 2 INTERMEDIATE value interaction locus with 3 input variables,

FIG. 60 illustrates an intermediate expression with 2 composite input variables,

FIG. 61 illustrates a threshold 2 expression with 3 composite input variables, and

FIG. 62 shows a threshold 3 expression with 3 composite input variables.

# DESCRIPTION OF THE PREFERRED EMBODIMENT

#### I. OVERVIEW

The present invention provides a new information processing system or representational environment which eliminates the need for synchronization means such as clocks, delay lines, or peripheral transition signaling means. The system itself provides a NULL (N) value which represents control. The NULL value is utilized as a flag of invalidity such that when it is asserted, data on a particular input is not valid. If, on the other hand, a nonNULL or data value is asserted, then the input is valid. The NULL value is added to the traditional binary values of TRUE (1) and FALSE (0) to yield a three-value logic system. Alternatively, the NULL value can be added to a single data value to yield a two-value logic system. In this case a dual-rail encoding can be used to obtain two data values necessary for conventional logic representations.

Since the representation of control is added as an extra value to the logic of an information processing circuit or unit itself, instead of in the form of an independent external 30 representation, the circuit is made autonomously determinable and the engineering coordination and synchronization complications associated with two independent representations are thus avoided. The circuits and information processing gates or members provided thereby autonomously 35 express their own completion of data resolution, thus enabling them to operate completely asynchronously in relation to each other.

An essential characteristic of such asynchronous transmission control is that events are controlled locally and are 40 no longer constrained to occur at specific times or during discrete intervals. Accordingly, circuit design is made more simple and straightforward. Moreover, this can be accomplished using standard binary logic.

As shown for example in the table below, the addition of 45 a NULL value to an existing logic circuit does not alter the established logic of the representation. For example, standard two-value logic gates are replaced by corresponding three-value logic gates. The NULL value indicates meaninglessness within the representation.

|     | N | 0 | 1 |   | N | 0  | 1 |   |     |  |

|-----|---|---|---|---|---|----|---|---|-----|--|

| N   | N | N | N | N | N | N  | N | N | N   |  |

| 0   | N | 0 | 0 | 0 | N | 0  | 1 | 0 | 1   |  |

| 1   | N | 0 | 1 | 1 | N | 1  | 1 | 1 | 1   |  |

| AND |   |   |   |   |   | OR |   |   | NOT |  |

The NULL value is added to the existing truth tables so that if either input to a gate is NULL, the output will be NULL. An input to a gate is VALID only when both inputs are nonNULL. An INVALID input is one with at least one 65 NULL value. As soon as both inputs are nonNULL, the input is valid and a nonNULL (DATA) value will be asserted. No

gate will assert a VALID output unless it's input is VALID. Each gate exhibits a distinct resolution event (the output transition from NULL to nonNULL) whenever a VALID input is presented to it. Each gate indicates the completion of it's own logical transformation process.

A practical example of the use of the NULL value convention is an AND logic gate implemented with a transistor circuit and having the three voltage values of +5, 0, and -5. If 0 is assigned to represent the NULL value, the -5 and +5 are VALID data values. When 0 is asserted to either input of the AND gate, the output will be forced to 0. If non-0 values (-5 or +5) are asserted on both inputs to the gate, the output is the logical AND of the two values the non-0 voltages represent. If 0 is never asserted (except perhaps in transition), then the gate acts just like a standard logic gate.

As previously discussed, the NULL value convention can also support single-data-value representations. Referring to the table below, this form of representation only has two values, NULL (N) and DATA (D). Two-value NULL convention logic is related to threshold logic. Since there is only one nonNULL value, data must be represented by quantities of DATA values. In the truth tables, D is DATA and N is NULL. For the threshold 1 table a single DATA value will set the output to DATA. For the threshold 2 table both inputs must be DATA for the output to be DATA.

Threshold 1 Threshold 2

In addition to utilizing the NULL value at the gate level of a circuit, the NULL value may also be utilized at the circuit level to indicate the proper transfer of data between circuits. The representation element that manages the presentation of data between two NULL convention logic circuits is called a boundary element. As shown in FIG. 1, null convention logic circuits bounded by such elements A and B behave as independently proceedable units that accept data, process it, and then pass it on to other circuits or units. The input data, in addition to expressing values, is either VALID or all-NULL, thus incorporating the control information necessary for determining it's representational validity

The assertion and presentation of value combinations involves a handshake protocol convention between two circuits. In the protocol of two control variables each with two values, the input data itself serves as one of the control variables. The input data in addition to expressing the values of the data is either VALID or all-NULL These two states of VALID and all-NULL in the data itself provide two values for one of the handshake variables. So the data stream itself becomes one of the handshake variables.

An input is received and stored in a current boundary element and stably asserted until the next boundary element can receive it. Then the current boundary element is freed up to receive another input. Data flows through a representation as packets from boundary element to boundary element. As discussed with respect to FIG. 1, between boundary elements there can be any NULL convention logic circuit that will perform some transform on the data. A NULL convention logic circuit bounded by boundary elements will cycle

through completely NULL states and completely VALID states so that the NULL convention criteria that allows determination of the completion of the resolution of a NULL convention logic circuit is satisfied.

Boundary elements can be associated in various structures, for example a simple pipeline structure. The pipeline is completely autonomous. A VALID input presented to the first element in the pipeline will begin a sequence of interactions that will propagate the data from element to element all the way through the pipeline. As each element sees a VALID input, it will receive it and assert it to the next element in the pipeline. Several data packets can be simultaneously propagating through the NULL convention pipeline just like any other pipeline. The propagation rate of the pipeline is determined by the longest transmission delay between two boundary elements. Boundary elements can also be associated in fan-in, fan-out, and circular configurations.

A VALID input at a circuit representing a desired process utilizing associated boundary elements will trigger the progression of events that is the represented process. As the events proceed, the circuit resets itself to be triggered again. As completed processing results arrive at the output of the circuit, their completion is signaled by the assertion at the output of the values comprising the completed processing results themselves.

Boundary elements are preferably used to partition a representation into discrete independently proceedable units that may be complex internally, but that have relatively simple interfaces between them. This allows many representational elements to be simultaneously operating, increasing the throughput of the circuit.

The system of the present invention can process data with NULL values via its information processing members (logic gates) that resolve combinations of data values. In contrast, the prior art technology can merely transmit an indeterminant value along with data values over transmission elements (wires, for example). As a result of this advantage the system is speed independent at every level in that the information processing units (circuits) and members (gates) of this system report their own completion.

The NULL convention logic system provides a representational environment in which autonomously acting and coordinated NULL convention logic circuits can implement independently acting and locally controlled process representations. External global control representations are not needed. The system of this invention is applicable to digital computers, telephone switching systems, and in a variety of control systems, particularly those amenable to asynchronous processing and control.

In the description below, process expression is discussed first in general terms (II), and then in greater detail to demonstrate the need for the NULL value convention in process expression, in terms of a process for resolving data 55 (III). The generally configurable process expression is then introduced, and particularly with respect to a system for manipulating and resolving data (IV). Finally the completion integrity of successive resolution cycles and the intermediate non-data value is discussed (V).

# II. A MODEL OF PROCESS EXPRESSION

This discussion introduces a model of process expression that focuses on the nature of process itself. The model will lay a foundation for exploring process expression.

Process is defined in very general terms then the invocation model of process expression is introduced. A series of 10

examples present the two domains of expression within the model and illustrate the fundamental principles of process expression.

#### A. PROCESS

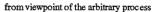

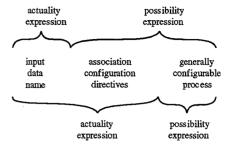

Process is change occurring to existential entities due to interactions among those entities. Process begins with the possibility of interactions among entities. There may be many possible interactions but each process is the actualization of only one possibility. Process is a confluence of possibility and actuality. All of the details of each possible interaction may be prespecified in detail before the fact, but which possible interaction will actually occur cannot be specified until the time of occurrence. The possibility and the actuality of a process are inherently separate aspects of the process and must be separately expressed. These aspects will be called the possibility expression and the actuality expression.

The possibility expression is an inherently incomplete specification of a process. It must defer as an open question the specification of which of the possible interactions will occur. The actuality expression provides the answer to this question and by combining with a possibility expression completes the specification of a particular interaction. The possibility and actuality expressions must correspond in the sense that the answer of the actuality expression must fulfill the question of the possibility expression. A computer and program is the possibility expression and data is the actuality expression.

#### B. THE INVOCATION MODEL

There must be existential entities. The entities must support a property of changeability in addition to their own existence. There must be a means of specifying how these entities associate to interact and them must be a means of specifying what changes accrue from interaction.

The existential entities will be called variables. A value is the nonexistential property of a variable that can change during interaction. Every variable is always asserting exactly one value. Variable association rules specify which variables can associate with each other to interact. Value transform rules specify which values can interact and how these values will change. The model consists of variables, values, variable association rules and value transform rules. Variables interactively associate according to variable association rules. Values asserted by the variables change according to value transform rules.

#### 1. Variable Association Rules

The variable association rules specify which variables can interact. If two or more variables are associated then those variables are interactively proximate. If variables are not associated by any association rule then they are not proximate and cannot interact.

The association rules differentiate the variables by specifying exactly how each variable is interactively proximate with one or more other variables. Each variable has a place in the process universe and each is differentiated by its place in relation to the other variables. If an association rule states that all variables are or may be in interactive proximity then each variable is in no particular place in relation to the other variables and there is no way to differentiate one variable from another. If an association rule states that no variables are associated then it doesn't matter whether variables can be differentiated, they cannot interact and are effectively nonexistent.

# 2. Value Transform Rules

The value transform rules specify what changes occur to interacting values. A value transform rule specifies a combination of values as the name of the rule and a set of result values. The combination of values that forms the name of a value transform rule specifies that that combination of values is interactively proximate and will interact. If a combination of values does not form the name of any value transform rule then that combination of values is not proximate and they will not interact. The result values of the rule specify the values that will result from the interaction.

Similarly to variables, values receive their differentiation and place in the interaction universe from the value transform rules. Only values that appear in value transform rule names are interactively proximate and then only in the combinations specified by the names. Values appearing both in value transform rule names and also as result values in other value transform rules form relationships among value transform rules that forge the structure of the value interaction universe and establish each value's place in it. A value is differentiated by its place in relation to all the other values in the process universe as specified by the set of value transform rules for the process.

#### 3. Primitive Process Interaction

A primitive process interaction occurs when an actuality expression arises and an interaction rule name is formed. This occurs when at least two variables are in interactive proximity and their values are in interactive proximity (the 30 values form the name of a value transform rule). If two variables are in interactive proximity but their values are not in interactive proximity (they do not form a value transform rule name) no interaction will occur. Conversely values can be interactively proximate but if their asserting variables are 35 not interactively proximate no interaction will occur.

The possibility expression of the process is a set of value transform rules and the existence of the variables. Each value transform rule is one possible interaction. The question of which possible interaction will proceed is posed by 40 the names of the rules. The question is which rule name will be formed.

The answer is provided when two or more variables become interactively proximate and their values form the name of one of the value transform rules. Like the sorcerer 45 invoking his demons by name to perform his magical transformations the named rule is invoked and the values are transformed. Hence the invocation model. The values of interactively proximate variables forming a transform rule name is the actuality expression for the interaction. It is the 50 delivery of the deferred specification, the answer to the question of which of the possible interactions will proceed.

#### 4. Interaction Composition

interaction is a progression of dependent interactions. The dependency relationships among the interactions are expressed as name formation dependency relationships. The name formed for one interaction depends on the result values of one or more other interactions. The dependency 60 relationship can be expressed as direct association relationship between each value of a name of one interaction and a result from another interaction that provides that value. It is still not possible to predetermine which transform name will be formed for each interaction but it can be predetermined 65 where the interaction's transform name will come from within the expression.

12

These dependency relationships form a network of association relationships of result values to name values among the interactions. This network of association relationships provides each interaction with a place in relation to all the other interactions.

FIG. 2 shows a network of association relationships with no cycles. Although any configuration of association relationships is possible, only association networks with no cycles are discussed in detail. Other association configurations will become apparent to those skilled in the art.

Each individual interaction is still expressed by its own possibility expression consisting of a set of value transform rules. These individual possibility expressions are combined into a larger composite possibility expression through the name formation dependency relationships. Most of the interactions receive their transform name values from specified local places in the structure of associations. A few name values, however, are not associated to any local places and they must come from someplace external to the structure of association relationships. These unassociated name values taken collectively are the composite actuality expression for the composite possibility expression. A composite actuality expression will also be referred to as the input name for the composite possibility expression. The result values of the composite possibility expression will be referred to as the result name.

The composite possibility expression is a complete stand alone specification of possibilities dependent only on its composite actuality expression. It is a larger self contained unit of expression (a possibility expression and an actuality expression) than the interaction.

These name formation dependency association relationships among interactions can be expressed within the invocation model either in terms of value transform rules or in terms of variable association rules. This means that the model possesses two quite different domains of expression.

# C. TWO DOMAINS OF EXPRESSION

The value transform rules and the variable association rules provide the model with two domains of differentiation and interactive association. A process can be expressed almost exclusively in terms of differentiation and interactive association of values by value transform rules or almost exclusively in terms of differentiation and interactive association of variables by variable association rules. Between these two extremes there is a large intermediate landscape of cooperative expression with gradations of expression from each domain.

# 1. Pure Value Expression

At one extreme all differentiation and interactive association is in terms of values and specified by value transform The next stage of process expression beyond a single 55 rules. There is no differentiation in terms of variable association rules. Variables are all simultaneously associated or they associate indiscriminately. There is no way from the point of view of interaction to tell one variable from another. All differentiation in the expression is by different values. All interactive association is specified by correspondence of unique values. This form of expression will be called a pure value expression.

> A natural example of this form of expression is a chemical reaction. The molecules are variables. The composition of each molecule determines its interaction possibilities and is its value. A liquid or gas is natures version of the association rule that specifies that there is no differentiation of variables.

The variables (molecules) will indiscriminately associate in the liquid or gas and there is no way to tell one variable from another except by the value it asserts. The molecules get together forming transform rule names and interact to form new molecular values. Another example of this form of 5 expression is subatomic particles. The variables (particles) indiscriminately associate in free space and there is no way to tell one variable (particle) from another except by the value it asserts. The particles get together forming transform rule names and interact to form new particles and composite 10 structures.

# 2. Pure Variable Expression

At the other extreme all differentiation and interactive 15 association is in terms of variables and specified by variable association rules. There is no differentiation in terms of value transform rules. There is a set of values and a set of value transform rules for all possible input names that those values can form. This means that all values are constantly in 20 interactive proximity. There is no way from the point of view of interaction to tell one value from another. All differentiation in the expression is by variable association. All interactive association is specified by specifically associated variables. This form of expression will be called a pure 25 variable expression.

A natural example of this form of expression is a network of neurons. The artificial computer is also primarily of this

Within the model there must always be a bit of each domain in every process expression. There must always be variables that associate and there must always be values that transform. Nevertheless the two ends of the territory will be referred to as pure value and as pure variable.

# 3. The Intermediate Expression Territory

Expression in the intermediate territory between pure value and pure variable is a cooperative endeavor between variable differentiation and value differentiation. A very simple example of this cooperative expression is the representation of numbers with different bases. Base two numbers have only two values and very simple value transform rules (logical truth tables) but have lots of digits that must be properly associated. Base ten numbers have ten values and 45 larger, more complex value transform rules (traditional addition and multiplication tables) but have fewer digits to be associated. These gradations of expression ranging from mostly in terms of value differentiation and value transform rules to mostly in terms of variable differentiation and 50 variable association rules will for convenience be called simply value expressions and variable expressions.

# D. VALUE EXPRESSION

In a value expression there is no differentiation of variables. All differentiation is in terms of values and specified by value transform rules. Transform rules will be represented in the format of the transform name followed by the result values enclosed in brackets, for example:

"name [result, result, . . .]."

Consider an example expression with 4 differentiated values A, B, C and D and two value transform rules that interactively associate those values. A and B interact and 65 completion of each stage is established by the presence of transform into D. C and D interact and transform into B. The two transform rules for the example are:

AB[D] or BA[D] CD[B] or DC[B]

The linear string representation makes it appear that ordering is significant when actually it is not. The input names AB and BA are equal and are both specified for this example. There can be no order relationships among the values because there can be no order relationships among the variables when they are interactively proximate. They are simply two values interacting. AB and BA are the same input name.

The value transform rule is the simplest most primitive form of process expression. No part of the rule can be reduced to simpler terms or be more precisely stated. The values are primitive and indivisible and the interaction result is complete in itself and unambiguous.

The value transform rules specify completely who does what with whom. As far as the variables are concerned anybody can do anything with anybody but in terms of the values only As can interact with Bs and only Cs can interact with Ds. As cannot interact with Ds nor Bs with Cs and so forth. There cannot be the A of this variable and the A of that variable because there is no this variable or that variable. Value difference is the only way to tell anything apart for this expression. A value expression can be elaborated and extended to more expressional complexity by adding more values and more value transform rules.

A pure value expression differentiates all parts of the expression by values. The input values form the name of a transform rule. The result specified by the transform rule is a different value from the input values so there is no ambiguity about when the interaction is complete. The input values disappear and the result values appear. The new value can form a new unique input name with other values and a new interaction can occur which results in new values which can form further unique input names and so on. The process progresses in a succession of fulfilled interaction possibilities determined by the formability of unique transform rule names. Each interaction possibility is dependent on one or more previous interactions to provide the values to form its input name. The set of transform rules below illustrates a value expression that proceeds in stages of unique input name formation dependencies.

| AB [C, D] |  |

|-----------|--|

| CC [D, E] |  |

| DD [G, F] |  |

| EF [F, G] |  |

| GG [X, Y] |  |

|           |  |

If there are some As and Bs present they will begin 55 interacting and generating Cs and Ds. The CC and DD interaction cannot occur until there are some Cs and Ds available. The CC and DD interactions will generate Es, Fs and Gs which will form the input names of the EF and GG, transforms will interact and finally produce Xs and Ys. For 60 this process the possibility expression is the set of value transform rules and the variable association rule that all variables are or will become interactively proximate. The actuality expression is the presence of the As and Bs.

The process is resolved in distinct discrete stages. The result values and the absence of input values for that stage. When Xs and Ys appear the resolution of the process is

completed. It is deterministic and directional. It can's run backwards and start generating As and Bs. All of these characteristics are determined solely by the differentiation and specific association of values as specified by the value transform rules.

### 1. Traditional Computation with Value Expressions

The value expression form is unfamiliar territory in the contemplation of process expression and computation. Traditional computation expresses results (numbers) in the 10 same form as the input was expressed (numbers). For the value expression this means that the results are expressed with the same values. This can lead to ambiguities in the direction of progression of resolution and indeterminability of completion. But the value expression form can accom- 15 modate these issues. The following examples will illustrate that the while the pure value end of the process expression landscape is associated mainly with natural expressions such as chemistry, physics and biology it is a fully capable computation environment.

There is in fact an important value expression system in the history of computational thought. This is the Roman numeral system without the subtractive principle. (This means that 9 is VIIII instead of IX). The digits of Roman numerals are generally presented in a certain order for convenient reading but without the subtractive principle the order has no significance to their meaning. No matter what arrangement the digits are presented in they represent the same number. Each digit of a number is a variable, each variable has a value. The variables have no particular association relationships among themselves. The meaning of each digit is differentiated entirely by its value. The magnitude of the number is determined solely by the values present.

| Possible values are:<br>Transform rules are: | M,D,C,L,X,V,I<br>IIII [V]     |

|----------------------------------------------|-------------------------------|

|                                              | VV [X]<br>XXXXX [L]<br>LL [C] |

|                                              | CCCCC [D]                     |

The only interactions possible in this Roman numeral expression are those specified by the value transform rules. Vs don's interact with Xs because there is no rule with the appropriate name. The above value transform rules are a complete expression of the process for addition in Roman numerals. Given two Roman numbers these rules will reduce them to a minimal single number representation. The numbers 1978 and 22 are used as examples.

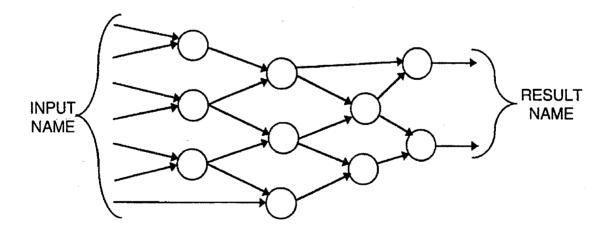

### MDCCCCLXXVIII XXII

To add the two numbers one simply throws them into a hypothetical bag and shakes as illustrated by FIG. 3. The bag 55 actions there has to be a guaranteed completeness to the itself is the variable association rule. It states that variables cannot wander off and that external variables cannot intrude. Shaking the bag specifies that all variables will eventually associate. There is no variable differentiation. Variables associate indiscriminately and there is no way to tell one 60 variable from another inside the bag except by its asserted value. The possibility expression is the set of value transform rules and the bag itself. The actuality expression is the values thrown into the bag.

The five is will eventually get together and form the name 65 IIII. This will invoke the value transform rule IIIII and the five Is will transform into a V. There are then two Vs which

will eventually make an X. The five Xs will make an L, the two Ls a C the five Cs a D and finally the two Ds an M. What remains in the bag are two Ms. No more interactions are possible because there are no value transform rules for Ms.

#### MDCCCCLXXVIII+XXII=MM

There are a couple of difficulties with this expression. First, it is not possible to determine when the expression inside the bag is fully resolved either from inside or outside the bag. Second, some of the transform rules require the confluence of five variables which might take a long time to occur. The Roman numeral system, however, was never intended to be autonomously resolving as it assumed a rather intelligent interpreter that could get all the proper variables together and could tell when its resolution was done.

The following examples will demonstrate that fully determinable autonomous expressions can be expressed in isolated pure value expression environments. So that the reader can more easily follow the examples the expressions from now on will be various forms of binary integer addition. The next example introduces the first form of this expression and is an expression whose transform rule names are never more than two values long.

| 25 | Possible values are | A,B,C,D,E |  |

|----|---------------------|-----------|--|

|    | Transform rules are | AA [B]    |  |

|    |                     | BB [C]    |  |

|    |                     | CC [D]    |  |

|    |                     | DD [E]    |  |

This expression behaves similarly to the Roman numeral expression. If it is assumed that A=1, B=2, C=4, D=8, E=16 it can be seen that these expressions are equivalent to binary numbers. A number is represented by specifying the appro-35 priate digits. As with the Roman numerals there is no significance to spatial arrangement of the variables. Numbers are added by throwing them in the bag and shaking.

#### DAC+BCA=EC: 13+7=20

This expression will complete more readily because no interaction requires the confluence of more than two variables but there is still no way to tell when the computation is completed. For an expression to establish its own com-45 pleteness there must be a distinct last interaction. With the current expression there might not even be a first interaction.

#### AC+BD=ABCD

Combining these two numbers directly results in a minimally represented number without any interactions at all. If no interactions occur there can be no last interaction to indicate completion.

To guarantee the completeness of a progression of interform of the values entering into the interactions. Completeness in this case means expressing the nonasserted place values as well as the asserted place values of the number. Another character will be attached to each value to indicate its assertion or nonassertion 1 means a value is asserted and 0 means it is not asserted so now AC would be represented as A1C1B0D0E0 or E0D0C1B0A1 since order does not matter. If each two characters such as A1 or B0 is considered a single value then the number of distinct values has simply been increased to achieve more expressional differentiation. The 2 character coding simply makes the meaning represented by each value more obvious to the reader.

20

30

17

Each input number must now be represented by five values and it can be guaranteed that there will be an interaction for each possible place value whether that place value is asserted or not. This is a mild form of a variable association rule specifying that variables are always present 5 in specific size groups and that each group has representative values from specific value groups. There is still, however, no order relationship imposed on the values.

For the new example the possible values are coded with two characters for convenience as follows:

| Possible values are: | E0,E1,D0,D1,C0,C1,B0,B1,A0,A1           |

|----------------------|-----------------------------------------|

| Transform            | . , , , , , , , , , , , , , , , , , , , |

| rules are:           | A0A0 [B0,A0] B0B0 [C0,B0]               |

|                      | A0A1 [B0,A1] B0B1 [C0,B1]               |

|                      | A1A0 [B0,A1] B1B0 [C0,B1]               |

|                      | A1A1 [B1,A0] B1B1 [C1,B0]               |

|                      | COCO [DO,CO] DODO [EO,DO]               |

|                      | COC1 [DO.C1] DOD1 [EO.D1]               |

|                      | C1C0 [D0,C1] D1D0 [E0,D1]               |

|                      | C1C1 [D1,C0] D1D1 [E1,D0]               |

|                      | E0E0 [E0]                               |

|                      | E0E1 [E1]                               |

|                      | E1E0 [E1]                               |

|                      | E1E1 [E0]                               |

|                      |                                         |

The integer addition example now looks like:

EO D1 C1 R0 A1+F0 D0 C1 R1 A1 =E1 D0 C1 R0 A0: 13+7=20

To resolve the expression one still just throws all the variables into a bag and shakes. As interact only with As, Bs with Bs, Cs with Cs, Ds with Ds and Es with Es. Each interaction generates a unique carry value which will interaction act with its corresponding values until no more interactions are possible. If the two input numbers are represented as five variables with each variable being a different one of the five flavors of value; Ax,Bx,Cx,Dx,Ex then the rules guarantee that the result will be a similar number of five variables. The  $_{40}$ form of the input name and result name is simply a convention among expressions.

Even with this completeness it is still not certain when the resolution of the process is complete. The E rule will be invoked twice, once for the input values and once for the 45 carry value from the D rule. There is no way to tell which invocation is the last one.

To eliminate the ambiguity separate rules and values must be specified for the input interactions and the carry interactions. Then there can be a definite last interaction which will 50 be the carry into the E interaction.

Because of minor combinatorial explosion in the possible values in this example they will be presented in two parts. The characters for the positional flavor and positional assertion are represented by two separate tables. For instance the 55 transform rule presented as AxAx[SBy,Az] when expanded in relation to the x x>>y z table really represents four separate transform rules: A0A0[SB0,A0], A0A1[SB0,A1], A1A0[SB0,A1] and A1A1[SB1,A0].

Possible

values are:

Dx,Cx,Bx,Ax UDx.UCx TDx,TCx,TBx SDx,SCx,SBx RDx,RCx,DONE x = 0,1 18

-continued

|                |                    | Precedence of  |

|----------------|--------------------|----------------|

|                |                    | occurrence     |

| Transform      |                    | relationships: |

| rules are:     | AxAx [SBy,Az]      | 1              |

|                | BxBx [SCy,TBz]     | 1              |

|                | SBxTBx [RCy,Bz]    | 2              |

|                | CxCx [SDy,TCz]     | . 1            |

|                | SCxRCx [ UCz]      | 3              |

|                | TCxUCx [RDy,Cz]    | 4              |

| 1              | DxDx [ TDz]        | 1              |

|                | RDxSDx [ UDz]      | 5              |

|                | TDxUDx [ Dz. DONE] | 6              |

| for all rules: | x x >> y z         | -              |

|                | 0 0>>0 0           |                |

|                | 0 1>>0 1           |                |

| i              | 1 0>> 0 1          |                |

|                | 1 1>>1 0           |                |

|                | 1 1>>1 0           |                |

The integer addition example now looks like:

E0D1C1B0A1+E0D0 C1B1 A1=E1 D0 C1 B0 A0 DONE

The new R, S, T and U values separately track the carry values and the carry interactions. The DxDx rule is the input interaction and the TDxUDx rule is the carry propagation into D which is necessarily the last interaction. The result looks just like the previous result except that a new result value, DONE, is confidently generated by the last interac-

All of the additional complexity of specification to achieve complete control is just a matter of more values and more value transforms that track intermediate values through the interactions to establish a consistent and regular behavior that possesses a distinct last interaction. No new concepts or primitive elements needed to be introduced. Control is not a primitive of process expression. It emerges from the defined expressional primitives properly arranged. It is simply extra expression beyond what is required to just transform the data.

A familiar process has been completely expressed with full generality in a pure value environment. The expression is complete and self contained. Given the values, the transform rules and the variables it will proceed quite independently and autonomously in an orderly progression of distinct interactions leading to a distinct last interaction which determines completion. There is no ambiguity in its behavior and it needs no external assistance to effect its resolution.

# E. NAME FORMATION DEPENDENCY RELATIONSHIPS

How an input name is expressed and resolved depends on the resolution resources available. The most critical resource for any expression is the value transform rules available. If a very large number of Value transform rules with names eight values long were available then the previous example expression could be resolved in a single interaction. The example used value transform rules with names only two values long. Consequently the expression could not be 60 resolved in a single interaction.

An input name that is too long to be resolved in a single interaction must be resolved a piece at a time by a necessarily dependent progression of multiple interactions each resolving a smaller input name which is a piece of the larger 65 input name. The eight value input name had to be broken up into 4 separate input interactions. The results of these input interactions must be combined to form input names for inner

interactions and so on until the proper result values for the eight value input name are determined. The inner interactions depend on the results of the input interactions to form their input names. This dependence of the formation of the input name for one interaction on the result of one or more other interactions is name formation dependency. Name formation dependency relationships for value expressions are expressed by value correspondence between result values and name values.

For a value expression this association of result to input name formation is expressed by value correspondence. In the last example above for instance the transform rule named RDxSDx is really 4 transform rules RD0SD0, RD0SD1, RD1SD0 and RD1SD1. Only one of these input names will be formed and the corresponding rule invoked. Which name is formed depends on the CxCx rule which will result in SD0 or SD1 and the TCxUCx rule which will result in RD0 or RD1. The results of these two interactions will form one of the four names of the RDxSDx rules. Within the context of the expression the values to form an RDxSDx name cannot come from anywhere else but the resolution of a CxCx interaction and of a TCxUCx interaction. The RDx of the RDxSDx transform name is a direct association to the RDx result value of the CxCx transform rules.

The precedence of occurrence relationships for the example as shown in the preceding TABLE and in FIG. 4 indicate the order in which the interactions can occur. This order is determined by the input name formation dependencies of the expression embodied in the transform rules. The 1 interactions can all occur simultaneously or at any time. Interaction 6 is guaranteed to be the last interaction. The input name formation dependency relationships in the expression fully represent all the possible concurrency. For instance the TCxTCx input name cannot be formed and the interaction will not occur before the CxCx and SCxRCx interactions occur. Even though the CxCx interaction can occur immediately the interactions dependent on it will not occur until CxCx occurs no matter when that is. The control expressed in the expression is complete and general. No matter how long it takes for each interaction to occur or how long it takes for the variables to get together, the expression will resolve correctly and completion of resolution can be determined by the assertion of the DONE value. The DONE value can perhaps open the bag and deliver the result.